# EE105 – Fall 2015 Microelectronic Devices and Circuits Multi-Stage Amplifiers

Prof. Ming C. Wu

wu@eecs.berkeley.edu

511 Sutardja Dai Hall (SDH)

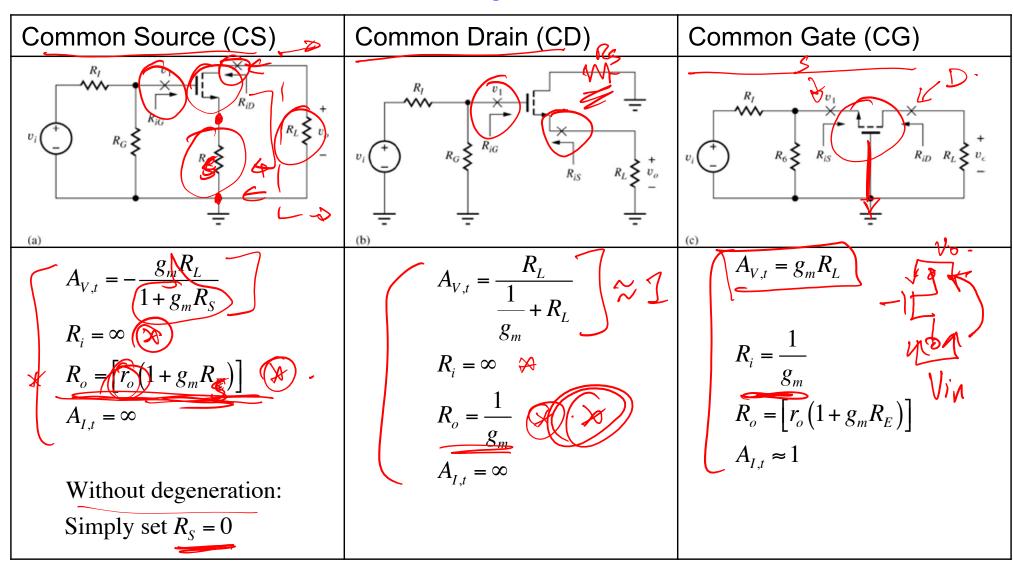

# Terminal Gain and I/O Resistances of MOS Amplifiers

For the gain, R<sub>i</sub>, R<sub>o</sub> of the whole amplifier, you need to include voltage/current dividers at input and output stages

# **Summary of MOS Single-Transistor Amplifiers**

|          | MOS            | Common<br>Source | Common<br>Source<br>with Deg. | Common<br>Drain | Common<br>Gate |

|----------|----------------|------------------|-------------------------------|-----------------|----------------|

| ( of Six | R              | 8                | 8                             | 8               | Small 😕        |

| M        | R <sub>o</sub> | Large            | Very Large                    | Small           | Large          |

| M        | A <sub>V</sub> | Moderate         | Small                         | ~ 1             | Moderate       |

| •        | f <sub>H</sub> | Small            | Moderate                      | Large           | Large          |

# Single Stage Amplifier Cannot Meet All Requirements

- For example, a general purpose operational amplifier requires

- High input resistance  $\sim 1M\Omega$

- Low output resistance ~ 100Ω

- High voltage gain ~ 100,000 √

- No single transistor amplifier can satisfy all spec's

- Cascading multiple stages of amplifiers offers a path towards the design

### **Multistage Amplifiers**

- Usually

- An input stage to provide required input resistance

- Middle stage(s) to provide gain

- An output stage to provide required output resistance or drive external loads

- More gain!

- Gain/stage limited, especially in nanoscale devices

- Improve Bandwidth

- De-couple high impedance nodes from large capacitors

- DC coupling (no passive elements to block the signal)

- Use amplifiers to naturally "level shift" signal

### Impedance "Match"

- On-chip circuits often use "voltage/current" matching to minimize loading

- Keep in mind the input resistance and output resistance of each type of stage so that the loading does not create an undesired effect

| - TA                       | _              |                        |

|----------------------------|----------------|------------------------|

|                            | Ideal $R_{in}$ | Ideal R <sub>out</sub> |

| Voltage Amplifier ∨ → ✓    | 8              | 0                      |

| Current Amplifier ➤ T → T  | 0              | $\infty$               |

| Transconductance Amplifier | 8              | ∞ <u>∠</u>             |

| Transresistance Amplifier  | 0              | 0                      |

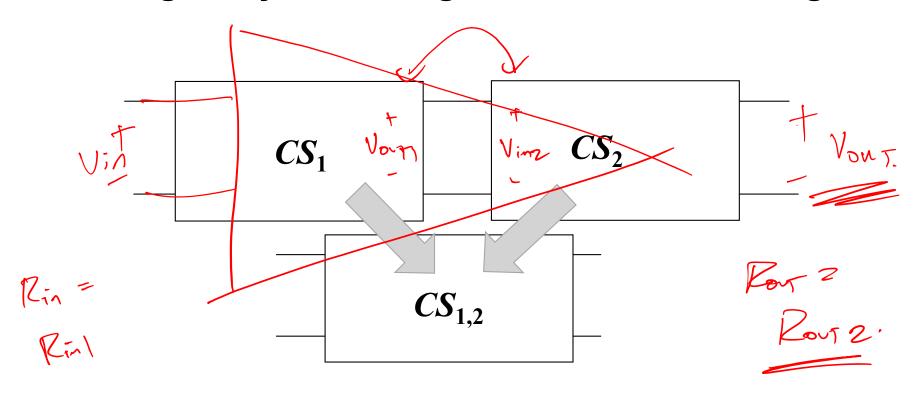

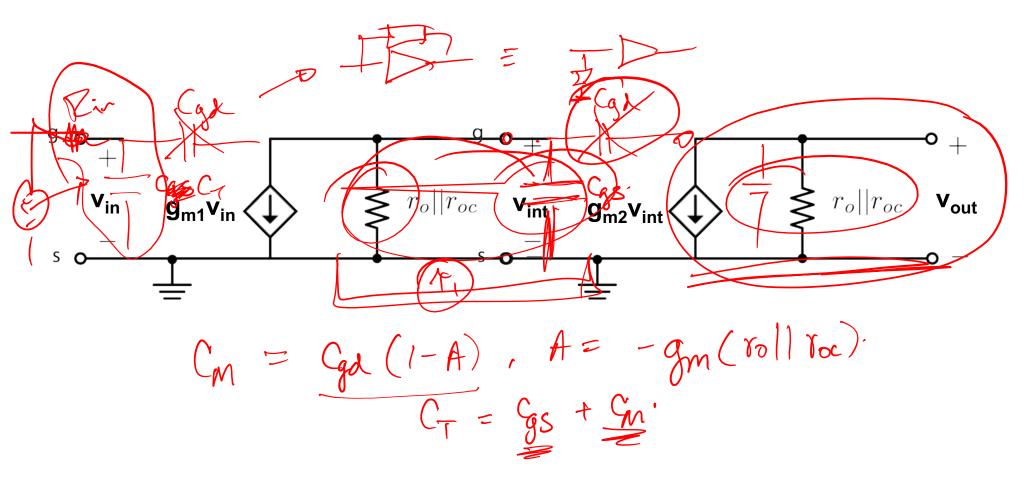

#### **Two-Stage Voltage Amplifier**

Boost gain by cascading Common-Source stages

Can combine into a single 2-port model Results of new 2-port:  $R_{in} = R_{in1}$ ,  $R_{out} = R_{out2}$

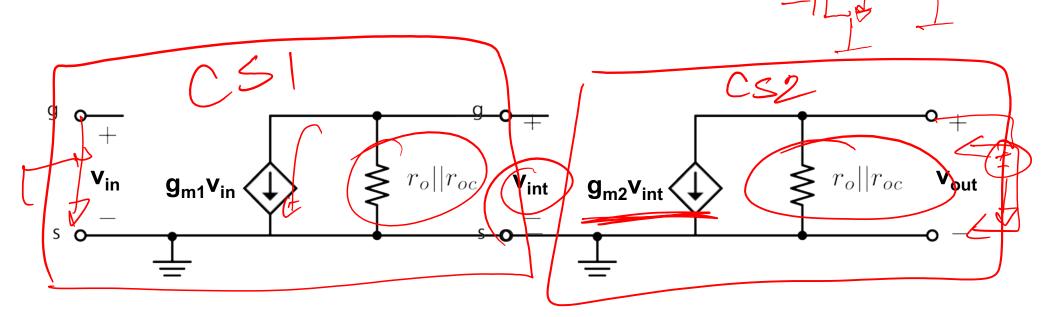

# **CS** Cascade Analysis

#### **Results of new 2-port:**

$$R_{in} = R_{in1} = \infty$$

$$R_{out} = R_{out2} = \text{ follow}$$

$$A_{V} = v_{out}/v_{in} = \text{ Virt } \text{ Vort } = (-g_{m1} \cdot (f_{o}||f_{oc}))$$

$$\text{Find } \text{ Find } \text$$

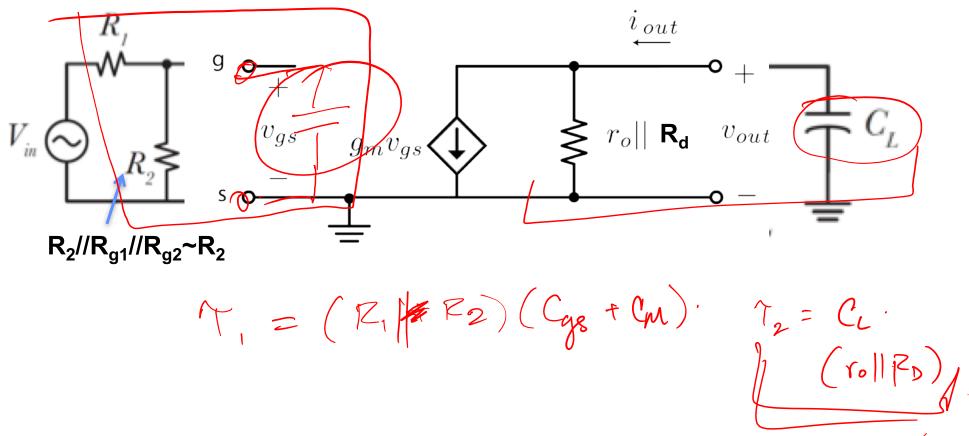

#### **CS Cascade Bandwidth**

#### Two time constants:

$$\tau_1 = \left( \begin{array}{c} C_{gs} + C_{m} \right) - \left( \begin{array}{c} \Gamma_{o} || \Gamma_{oc} \end{array} \right) \\ \tau_2 = 0 \quad \text{M}$$

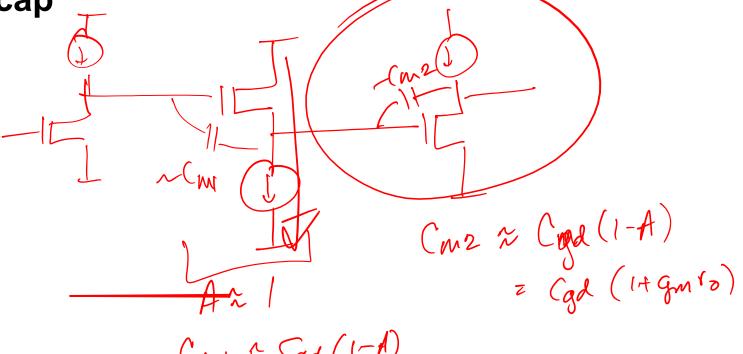

#### **Bandwidth Extension**

Common Source stage has high gain, but low bandwidth

Note that Miller effect is the culprit

Follower stage can buffer source resistance from

Miller cap

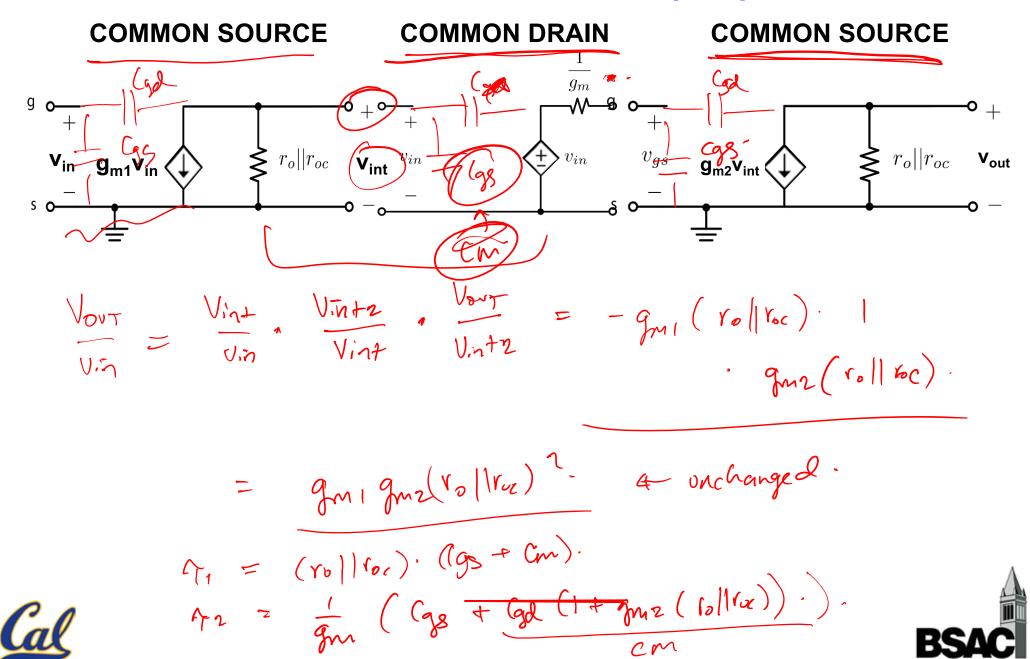

# **Bandwidth Extension Using Source Follower (SF)**

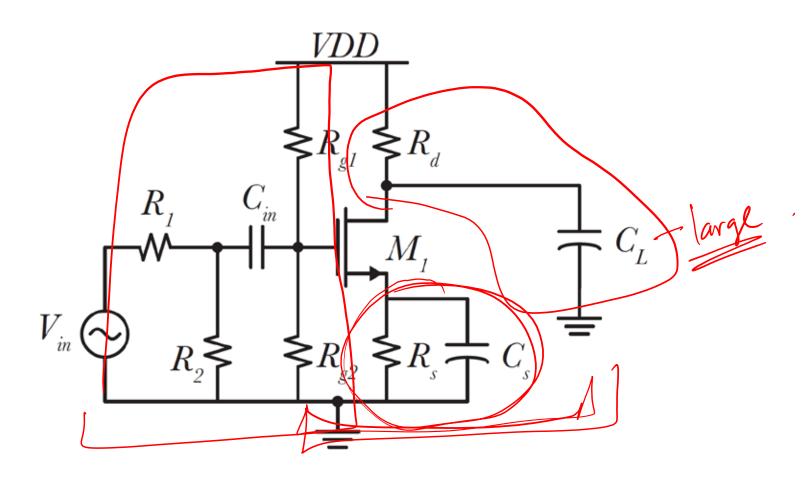

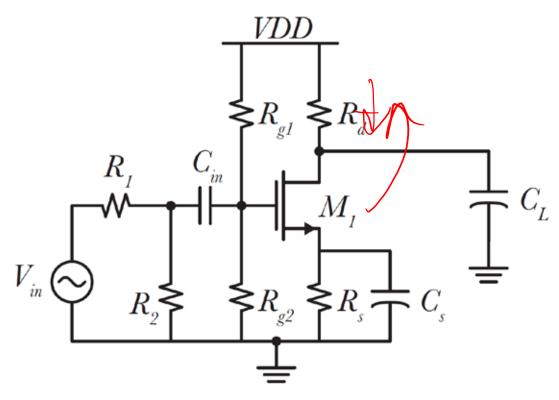

### **CS Example with Cap Load**

- C<sub>in</sub> and C<sub>s</sub> are very large, therefore they look like short circuits to the AC signal.

- If C<sub>L</sub> is very large, its pole dominates, let's analyze

### **CS with Cap Load – Small Signal**

- What are the time constants associated with the capacitors in this circuit?

- What can we do if we have to drive a large C<sub>L</sub>?

#### **CS** with Cap Load – Bandwidth

- How can we reduce the impact of C<sub>L</sub>?

- One way is to reduce the resistance R<sub>d</sub>, but this reduces our low-frequency gain

- To recover the gain we can increase  $g_{m1}$ .

What does this cost us?

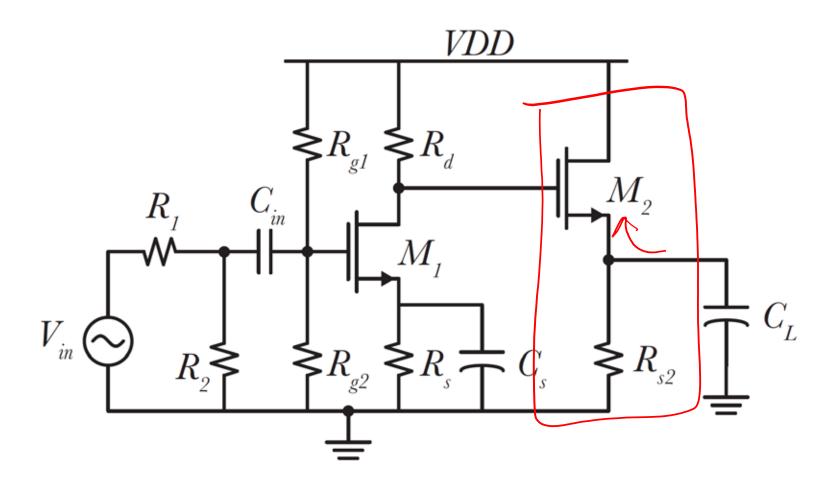

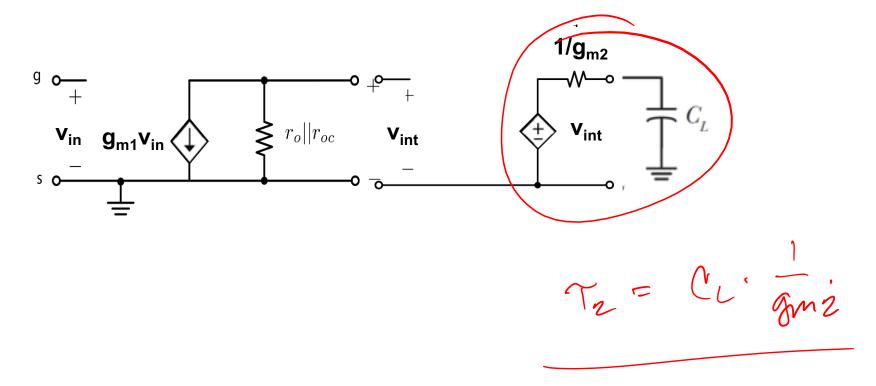

#### **CS** with Cap Load – BW Extension

A better way to extend the bandwidth is to add a sourcefollower stage.

Similar to previous example

#### **CS** with Cap Load – BW Extension

- By adding a CD (Source Follower) we can increase the bandwidth

- It costs us power for the CD stage

- Remember that increasing the BW by increasing g<sub>m1</sub> costs us

much more

- Common source provides gain, CG acts as a buffer, but is it even helping?

- How do you bias this circuit?

High Rout.

Headroom problems

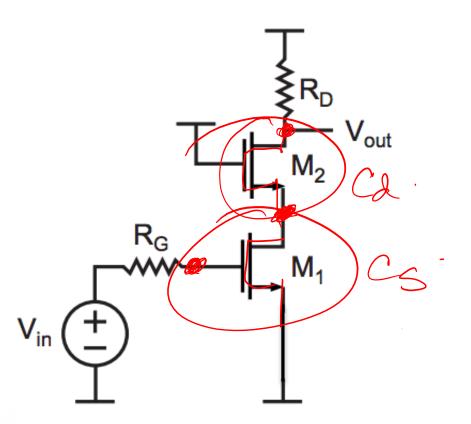

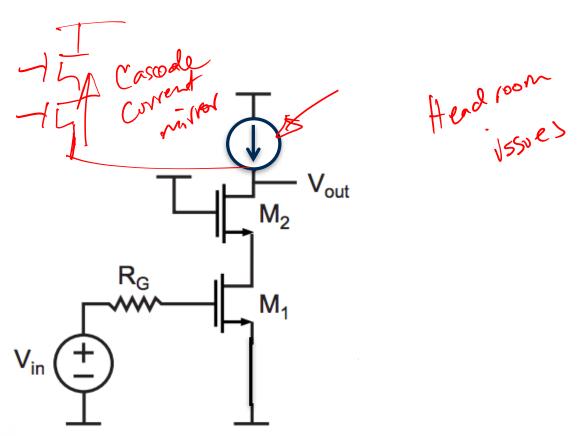

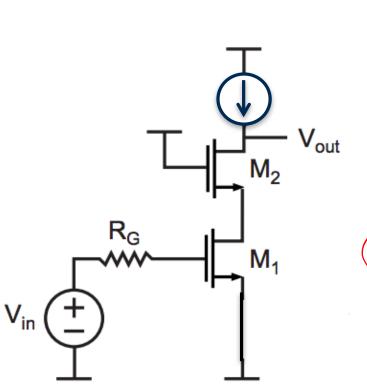

## Merged CS + CG = Cascode

Let's apply 2-port small-signal analysis

- In this case, we care about the input current to the second stage

- Note that the input resistance of the CG is low, therefore the majority of the CS current is fed to the CG

•

$$A_v = \frac{V_{ovt}}{V_{in}} = \frac{7_{in}}{V_{ovt}} =$$

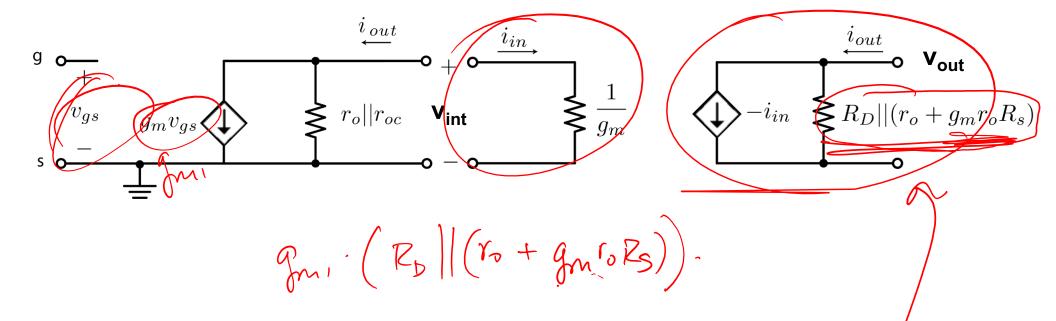

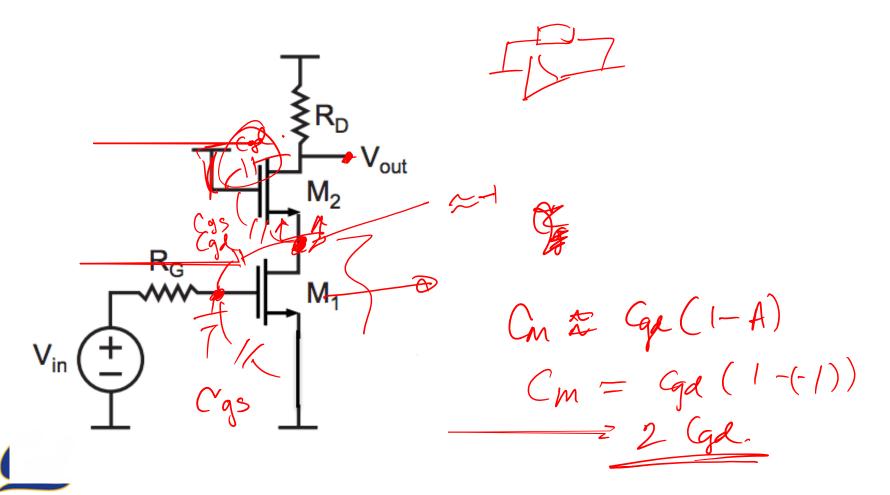

#### **Cascode Bandwidth**

- Draw in the C<sub>gs</sub> and C<sub>gd</sub> capacitors.

- Which ones are Miller effected?

- Is this better or worse than a CS without a CG?

#### **Cascode Bandwidth**

Draw in the capacitors and input resistance

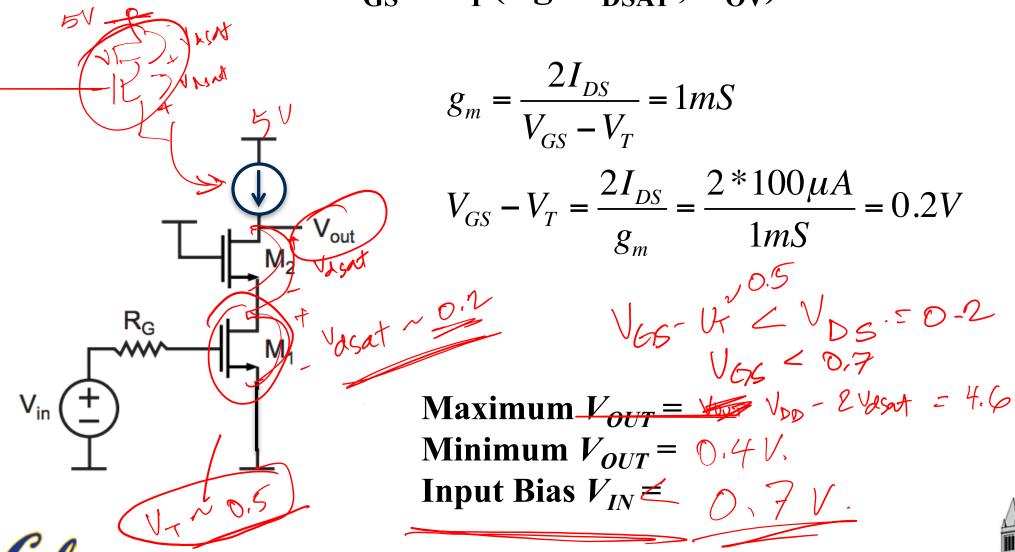

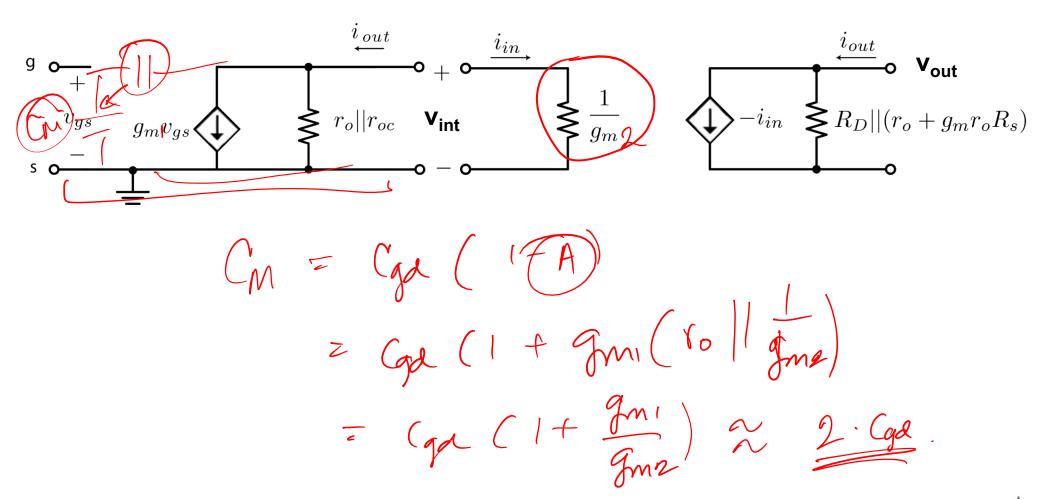

#### **Cascode Biasing**

- CG has a very large output resistance

- Loading it with R<sub>D</sub> is likely to reduce the voltage gain

- We can increase the gain by using a current source load, but r<sub>oc</sub> needs to be very large. Can use a cascode current mirror!

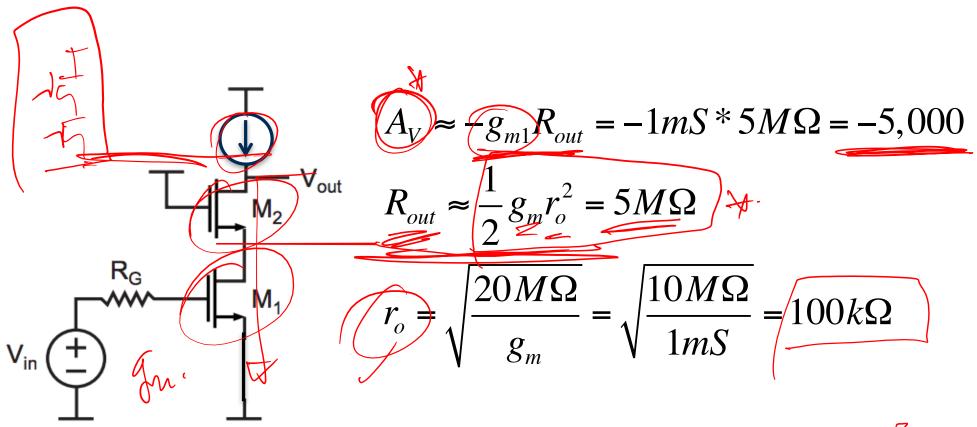

### **Complete Amplifier Design**

Goals:  $g_{m1} = 1 \text{ mS}, R_{out} = 5 \text{ M}\Omega$

For simplicity, let's assume all  $g_m$  and  $r_o$  values are equal

Av = Gon, Bout = gmigmz Room 15.

#### **Bias Current & Device Sizing**

Need to know process parameters to solve for W/L

$$k' = 100 \mu A/V^2$$

$$\lambda = 0.1 \, [V^{-1}]$$

$$r_o = \frac{1}{\lambda I_{DS}} = 100k\Omega$$

$$I_{DS} = \frac{1}{.1V^{-1} * 100k\Omega} \neq 100\mu A$$

$$g_{m} = \sqrt{2k' \left(\frac{W}{L}\right)} I_{DS} = 1mS$$

$$\frac{W}{L} = \frac{g_m^2}{2k'I_{DS}} = \frac{(1mS)^2}{2*100\mu*100\mu A} = 50$$

### **Output (Voltage) Swing**

Need to know  $V_{GS} - V_T$  (e.g.  $V_{DSAT}$ ,  $V_{OV}$ )